### HORNET SERIES (ORG14xx) FULLY INTEGRATED GPS MODULE

Datasheet

Origin GPS.com

### **INDEX**

| Datashe | eet                                         |    |

|---------|---------------------------------------------|----|

| 1.      | SCOPE                                       | 5  |

| 2.      | DISCLAIMER                                  | 5  |

| 3.      | SAFETY INFORMATION                          | 5  |

| 4.      | ESD SENSITIVITY                             | 5  |

| 5.      | CONTACT INFORMATION                         | 5  |

| 6.      | RELATED DOCUMENTATION                       | 5  |

| 7.      | REVISION HISTORY                            | 6  |

| 8.      | GLOSSARY                                    | 6  |

| 9.      | ABOUT HORNET FAMILY                         |    |

| 10.     | ABOUT ORIGINGPS                             | 7  |

| 11.     | DESCRIPTION                                 | 8  |

| 11.1.   | FEATURES                                    | 8  |

| 11.2.   | ARCHITECTURE                                | 9  |

| 11.3.   | APPLICATIONS                                | 11 |

| 12.     | ELECTRICAL SPECIFICATIONS                   | 12 |

| 12.1.   | ABSOLUTE MAXIMUM RATINGS                    | 12 |

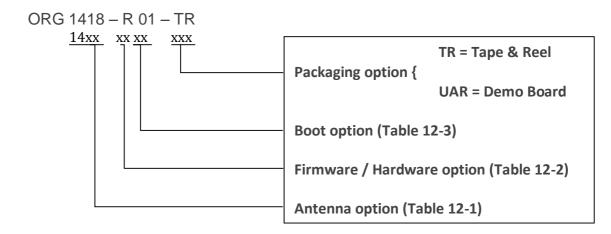

| 12.2.   | RECOMMENDED OPERATING CONDITIONS            | 12 |

| 13.     | PERFORMANCE                                 | 14 |

| 13.1.   | ACQUISITION TIMES                           | 14 |

| 13.2.   | SENSITIVITY                                 | 14 |

| 13.3.   | RECEIVED SIGNAL STRENGTHS                   | 15 |

| 13.4.   | POWER CONSUMPTION                           | 15 |

| 13.5.   | ACCURACY                                    | 16 |

| 13.6.   | DYNAMIC CONSTRAINS                          | 16 |

| 14.     | POWER MANAGEMENT                            | 17 |

| 14.1.   | POWER STATES                                | 17 |

| 14.2.   | POWER SAVING MODES                          | 17 |

| 15.     | EXTENDED FEATURES                           | 20 |

| 15.1.   | ALMANAC BASED POSITIONING (ABP™)1           | 20 |

| 15.2.   | ACTIVE JAMMER REMOVER                       | 20 |

| 15.3.   | CLIENT GENERATED EXTENDED EPHEMERIS (CGEE™) |    |

| 16.     | INTERFACE                                   | 21 |

| 16.1.   | PAD ASSIGNMENTS                             |    |

| 16.2.   | CONNECTIVITY                                | 21 |

|         | POWER                                       |    |

|         | HOST CONTROL INTERFACE                      |    |

| 16.2.3. | HOST DATA INTERFACE                         |    |

| 16.2.4. | SMART SENSORS DATA INTERFACE                | 26 |

| 16.3.   | TYPICAL APPLICATION CIRCUIT                 | 27 |

| 17.     | PCB LAYOUT                                  | 28 |

| 17.1.   | FOOTPRINT                                   | 28 |

| 17.2.   | DESIGN RESTRICTIONS                         | 29 |

| 17.3.   | PLACEMENT                                   |    |

| 17.4.   | PCB STACK UP                                |    |

| 18.     | OPERATION                                   |    |

| 18.1.   | STARTING THE MODULE                         |    |

| 18.2.   | VERYFING THE MODULE HAS STARTED             |    |

| 18.3.   | SHUTTING DOWN THE MODULE                    |    |

| 19.     | SOFTWARE FUNCTIONS                          |    |

| 19.1.   | NMEA                                        |    |

| 19.2.   | OSP™                                        |    |

| 20.     | HANDLING INFORMATION                        |    |

| 20.1.   | PRODUCT PACKAGING AND DELIVERY              | 38 |

| 20.2.        | MOISTURE SENSITIVITY                                                     |    |

|--------------|--------------------------------------------------------------------------|----|

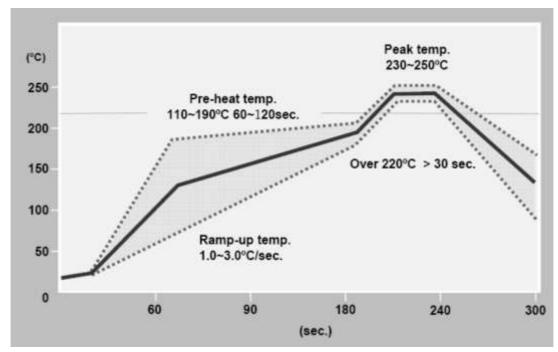

| 20.3.        | ASSEMBLY                                                                 | 39 |

| 20.4.        | REWORK                                                                   | 40 |

| 20.5.        | ESD SENSITIVITY                                                          | 40 |

| 20.6.        | COMPLIANCES                                                              |    |

| 20.7.        | SAFETY INFORMATION                                                       | 40 |

| 20.8.        | DISPOSAL INFORMATION                                                     |    |

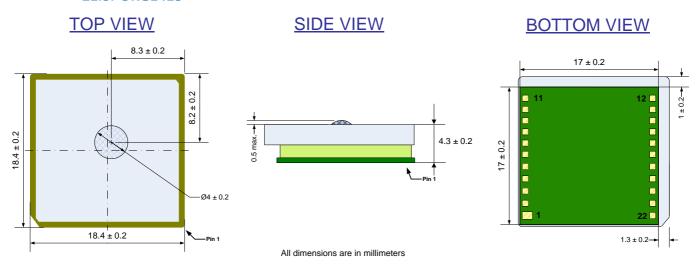

| 21.          | MECHANICAL SPECIFICATIONS                                                | 41 |

| 21.1.        | ORG1400                                                                  |    |

| 21.2.        | ORG1415                                                                  |    |

| 21.3.        | ORG1418                                                                  |    |

| 22.          | ORDERING INFORMATION                                                     |    |

| 23.          | DESIGN-IN CHECKLIST                                                      |    |

| 23.1.        | MODULE SELECTION                                                         |    |

| 23.2.        | SCHEMATICS VALIDATION                                                    |    |

| 23.3.        | LAYOUT VALIDATION                                                        | 45 |

|              |                                                                          |    |

|              |                                                                          |    |

| TAR          | BLE INDEX                                                                |    |

|              | E 1 – RELATED DOCUMENTATION                                              | -  |

|              |                                                                          |    |

|              | 2 – REVISION HISTORY                                                     |    |

|              | 3 – ABSOLUTE MAXIMUM RATING                                              |    |

|              | E 4 – STANDARD AND PREMIUM SERIES OPERATING CONDITIONS                   |    |

|              | 5 – BASIC SERIES OPERATING CONDITIONS                                    |    |

|              | E 6 – ACQUISITION TIMES                                                  |    |

|              | 7 – SENSITIVITY                                                          |    |

|              | E 8 – RECEIVED SIGNAL STRENGTH                                           |    |

|              | E 9 – STANDARD AND PREMIUM SERIES POWER CONSUMPTION @ Vcc = 2V (AVERAGE) |    |

|              | E 10 – BASIC SERIES POWER CONSUMPTION @ Vcc = 1.8V (AVERAGE)             |    |

|              | 11 – ACCURACY                                                            |    |

|              | 12 – DYNAMIC CONSTRAINS                                                  |    |

|              | 13 – ORG14XX PIN-OUT                                                     |    |

|              | 14 – UART BAUD RATE TOLERANCE                                            |    |

|              | 15 – SPI TIMING                                                          |    |

|              | 16 – HARDWARE OPTION                                                     |    |

|              | 17 – STARTUP TIMING                                                      |    |

|              | 18 – NMEA PROTOCOL OUTPUT MESSAGES                                       |    |

|              | 19 – NMEA PROTOCOL INPUT MESSAGES                                        |    |

|              | 20 – OSP BINARY OUTPUT MESSAGES                                          |    |

|              | 21 – OSP BINARY INPUT MESSAGES                                           |    |

|              | 22 – OSP BINARY INPUT MESSAGES                                           |    |

|              | E 23 – OSP BINARY INPUT MESSAGES                                         |    |

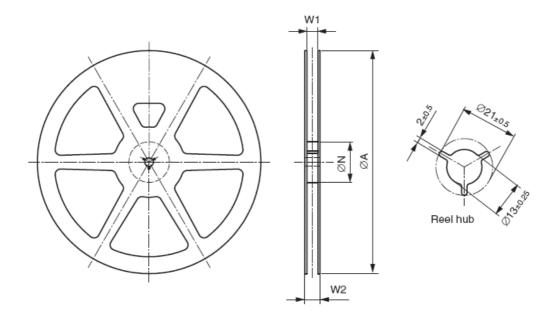

|              | 24 – CARRIER DIMENSIONS [mm]                                             |    |

|              | E 25 – REEL DIMENSIONS [mm]                                              |    |

|              | 26 – REEL QUANTITY                                                       |    |

|              | 27 – ORG1400 MECHANICAL INFORMATION                                      |    |

|              | E 28 – ORG1415 MECHANICAL INFORMATION                                    |    |

|              | E 29 – ORG1418 MECHANICAL INFORMATION                                    |    |

|              | 30 – FIRMWARE / HARDWARE OPTIONS                                         |    |

| <b>TABLE</b> | 31 – BOOT OPTIONS                                                        | 44 |

### **FIGURE INDEX**

| FIGURE 1 – ORG14XX ARCHITECTURE                   | 9  |

|---------------------------------------------------|----|

| FIGURE 2 – GSD4e FUNCTIONAL BLOCK DIAGRAM         | 10 |

| FIGURE 3 – ATP™ TIMING                            |    |

| FIGURE 4 – PTF™ TIMING                            |    |

| FIGURE 5 – APM™ TIMING                            |    |

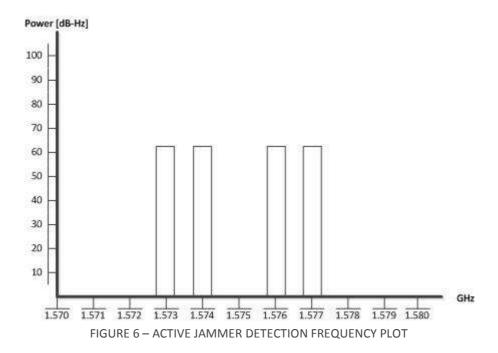

| FIGURE 7 – ACTIVE JAMMER DETECTION FREQUENCY PLOT | 20 |

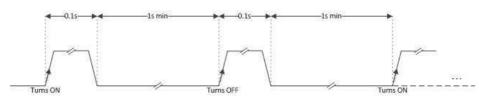

| FIGURE 8 – RECOMMEND ON OFF TIMING                | 23 |

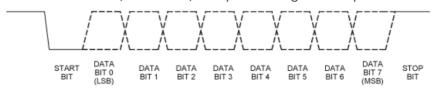

| FIGURE 9 – UART INTEGRITY                         | 24 |

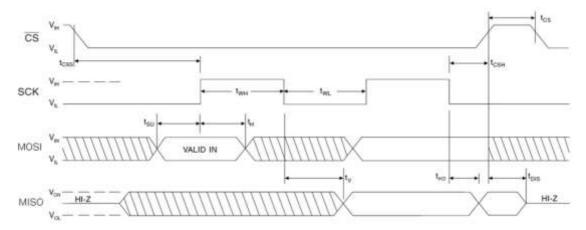

| FIGURE 10 – SPI TIMING                            |    |

| FIGURE 11 – UART INTERFACE CIRCUIT                | 27 |

| FIGURE 12 – SPI INTERFACE CIRCUIT                 | 28 |

| FIGURE 13 – FOOTPRINT                             |    |

| FIGURE 15 – TYPICAL PCB STACK UP                  |    |

| FIGURE 16 – STARTUP TIMING                        |    |

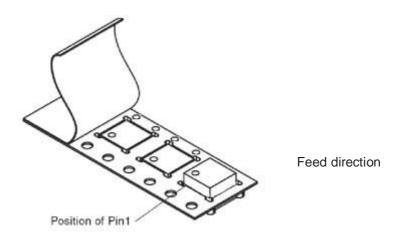

| FIGURE 17 – CARRIER                               |    |

| FIGURE 18 – MODULE POSITION                       | 38 |

| FIGURE 19 – RECOMMENDED SOLDERING PROFILE         | 40 |

| FIGURE 20 – ORG1400 MECHANICAL DRAWING            |    |

| FIGURE 21 – ORG1415 MECHANICAL DRAWING            |    |

| FIGURE 22 – ORG1418 MECHANICAL DRAWING            | 42 |

### 1. SCOPE

This document describes the features and specifications of Hornet series ORG14XX Modules.

### 2. DISCLAIMER

All trademarks are properties of their respective owners.

Performance characteristics listed in this document do not constitute a warranty or guarantee of product performance. OriginGPS assumes no liability or responsibility for any claims or damages arising out of the use of this document, or from the use of integrated circuits based on this document.

OriginGPS assumes no liability or responsibility for unintentional inaccuracies or omissions in this document. OriginGPS reserves the right to make changes in its products, specifications and other information at any time without notice.

OriginGPS reserves the right to conduct, from time to time, and at its sole discretion, firmware upgrades. As long as those FW improvements have no material change on end customers, PCN may not be issued. OriginGPS navigation products are not recommended to use in life saving or life sustaining applications.

### 3. SAFETY INFORMATION

Improper handling and use can cause permanent damage to the product.

### 4. ESD SENSITIVITY

This product is ESD sensitive device and must be handled with care.

### 5. CONTACT INFORMATION

Support - <u>info@origingps.com</u> or <u>Online Form</u>

Marketing and sales - <u>marketing@origingps.com</u>

Web - www.origingps.com

### 6. RELATED DOCUMENTATION

| Nº | DOCUMENT NAME                                                                     |

|----|-----------------------------------------------------------------------------------|

| 1  | Micro Spider – ORG4475 Evaluation Kit Datasheet                                   |

| 2  | Micro Spider – ORG4475 Product Change Notification                                |

| 3  | Spider and Hornet - Software User Manual for CSR® based receivers                 |

| 4  | Spider and Hornet - NMEA Protocol Reference Manual for CSR® based receivers       |

| 5  | Spider and Hornet - One Socket Protocol Reference Manual for CSR® based receivers |

| 6  | Spider and Hornet - Host Interface Application Note                               |

| 7  | Spider and Hornet - Low Power Modes Application Note                              |

| 8  | Spider and Hornet - Jammer Detector and Remover Application Note                  |

| 9  | Spider and Hornet - Client Generated Extended Ephemeris Application Note          |

| 10 | Spider and Hornet - Server Generated Extended Ephemeris Application Note          |

| 11 | Spider and Hornet - Ephemeris Push Application Note                               |

TABLE 1 - RELATED DOCUMENTATION

### 7. REVISION HISTORY

| REVISION | DATE             | CHANGE DESCRIPTION |

|----------|------------------|--------------------|

| B01      | January 1, 2012  | First release      |

| 2.0      | January 14, 2015 | Format update      |

| 3.0      | June 5, 2016     | Power Modes update |

TABLE 2 - REVISION HISTORY

### 8. GLOSSARY

A-GNSS Assisted GNSS

**BPF B**and **P**ass **F**ilter

**CE** European Community conformity mark

**CGEE™** Client **G**enerated **E**xtended **E**phemeris

CMOS Complementary Metal-Oxide Semiconductor

COMPASS PRC GNSS (same as BDS BeiDou-2 Navigation Satellite System)

EGNOS European Geostationary Navigation Overlay Service

**EMC** Electro-Magnetic Compatibility

ESD Electro-Static Discharge

**EVB E**valuation **B**oard

**EVK E**valuation **K**it

**FCC** Federal Communications Commission

**GALILEO EU GNSS**

GLONASS Global Navigation Satellite System

GNSS Global Navigation Satellite System

**GPS** Global Positioning System

I<sup>2</sup>C Inter-Integrated Circuit

IC Integrated Circuit

ISO International Organization for Standardization

LDO Low Dropout regulator

LGA Land Grid Array

LNA Low Noise Amplifier

MSAS Multi-functional Satellite Augmentation System

MSL Moisture Sensitivity Level

NFZ™ Noise-Free Zones System

NMEA National Marine Electronics Association

MEMS MicroElectroMechanical Systems

PCB Printed Circuit Board

PPS Pulse Per Second

QZSS Quasi-Zenith Satellite System

REACH Registration, Evaluation, Authorisation and Restriction of Chemical substances

RF Radio Frequiency

RHCP Right-Hand Circular Polarized

RoHS Restriction of Hazardous Substances directive

ROM Read-Only Memory

RTC Real-Time Clock

SAW Surface Acoustic Wave

SBAS Satellite-Based Augmentation Systems

SGEE™ Server Generated Extended Ephemeris

SIP System In Package

SMD Surface Mounted Device

SMT Surface-Mount Technology

SOC System On Chip

SPI Serial Peripheral Interface

TCXO Temperature-Compensated Crystal Oscillator

TTFF Time To First Fix

TTL Transistor-Transistor Logic

UART Universal Asynchronous Receiver/Transmitter

WAAS Wide Area Augmentation System

### 9. ABOUT HORNET FAMILY

Hornet family is offering the industry's smallest fully-integrated, highly-sensitive GPS and GNSS modules with integrated antennas or on-board RF connectors.

Hornet family features OriginGPS' proprietary NFZ™ technology for high sensitivity and noise immunity even under marginal signal condition, commonly found in urban canyons, under dense foliage or when the receiver's position in space rapidly changes.

Hornet family enables the shortest TTM (Time-To-Market) with minimal design risks.

Just connect power supply on a single layer PCB.

### 10. ABOUT ORIGINGPS

OriginGPS is a world leading designer, manufacturer and supplier of miniature positioning modules, antenna modules and antenna solutions.

OriginGPS modules introduce unparalleled sensitivity and noise immunity by incorporating Noise Free Zone system (NFZ™) proprietary technology for faster position fix and navigation stability even under challenging satellite signal conditions.

Founded in 2006, OriginGPS is specializing in development of unique technologies that miniaturize RF modules, thereby addressing the market need for smaller wireless solutions.

### 11. DESCRIPTION

OriginGPS has researched and enhanced the performance of standard GPS receivers in real life applications. OriginGPS in-house designed Microstrip Patch antennas with highest GPS-band performance and notch filtering for out-of band signals provides high selectivity. Furthermore, combined with internal RF shield and ground plane the ORG14XX series modules reveal excellent noise immunity and exceptional sensitivity. These carefully selected key components resulted in higher sensitivity, faster position fix, navigation stability and operation robustness under rapid environmental changes creating hard-to-achieve laboratory performance in heavy-duty environment.

### 11.1. FEATURES

- ➡ Stand alone operation

- OriginGPS Noise Free Zone System (NFZ™) technology

- ➡ Integrated proprietary microstrip patch antenna element

- ➡ Integrated LNA, SAW Filter, DC-DC buck regulator1, I/O Buffers1, TCXO and RTC

- **+** SiRFstarIV<sup>™</sup> GSD4e GPS processor

- + L1 (1575MHz) frequency, C/A code

- **+** 48 track verification channels

- → Navigation sensitivity: -160dBm

- ➡ Tracking sensitivity: -163dBm for indoor fixes

- < 35s under Cold Start conditions

- ★ Fast TTFF: < 1s under Hot Start conditions</p>

- Multipath mitigation and indoor tracking

- + Active jammer remover: tracks up to 8 CW interferers and removes jammers up to 80dB-Hz

- → SBAS (WAAS, EGNOS, MSAS) support2

- → Assisted GPS (A-GPS) support

- → Almanac Based Positioning (ABP™)2

- Client Generated Extended Ephemeris (CGEE™) and Server Generated Extended Ephemeris (SGEE™) for very fast TTFFs are supported through SiRFInstantFix™ and SiRFInstantFixII™

- **★** Automatic and user programmable power saving scenarios: ATP<sup>™</sup>, PTF<sup>™</sup>, APM<sup>™</sup>

- **+** Low power consumption: <20mW during ATP™

- → ARM7 109MHz baseband CPU

- → Smart sensor I<sup>2</sup>C master interface2

- → UART host interface, SPI optionally3

- ➡ Programmable UART protocol and messages rate

- → Selectable NMEA or OSP (SiRF Binary) communication standards

- ➡ Single voltage supply: wide input range1 2V 6V with UVLO or 1.8V

- → Ultra small footprint: 17mm x 17mm

- → Surface Mount Device (SMD)

- ➡ Industrial operating temperature range: -400 to 85°C

- → Pb-Free RoHS compliant

### Notes:

- 1. Not available in Basic series

- 2. Available in Premium series only

- 3. Different ordering codes for SPI

### 11.2. ARCHITECTURE

# ORG14XX SYSTEM CONFIGURATION 1.8V/2-6V Supply ON\_OFF ON\_OFF

FIGURE 1 - ORG14XX ARCHITECTURE

### **†** Microstrip Patch Antenna

OriginGPS integrated microstrip patch antenna element collects signals at 1575 MHz from the medium and blocks out-of-GPS L1 band frequencies.

### **+** ESD Protection Device

ESD TVS diode provides protection for module circuitry from high voltage transients on embedded antenna.

### **★** Band-Pass SAW Filter

Band-pass SAW filter eliminates inter-modulated out-of-band signals that may corrupt GPS receiver performance.

### **+** LNA (Low Noise Amplifier)

The integrated LNA amplifies the GPS signal to meet RF down converter input threshold.

Noise Figure optimized design was implemented to provide maximum sensitivity.

### **→** DC-DC Voltage Regulator

The high efficiency synchronous DC-DC step-down switch mode converter provides regulated voltage supply for GPS processor over wide input voltage range.

The design of this section was optimized for low ripple, low quiescent current and high PSRR.

### **TCXO** (Temperature Compensated Crystal Oscillator)

This highly stable 16.369 MHz oscillator controls the down conversion process in RF block of the GPS processor. Highest characteristics of this component are important factors in sensitivity, fast TTFF and navigation stability.

### → RTC (Real Time Clock) crystal

This miniature component with very tight specifications is necessary for maintaining Hot Start and Warm Start capabilities.

### → POR (Power-On Reset) Generator

This low quiescent current supervisory circuit monitors voltage domains and provides trigger signal for module power-up.

### **±** EEPROM (Electrically Erasable Programmable Read-Only Memory)

The 1Mbit serial EEPROM device provides local storage for Client Generated and Server Generated Extended Ephemeris data as well as for patches for GPS processor ROM firmware.

### ➡ RF Shield

RF enclosure avoids external interference to compromise sensitive circuitry inside the receiver. RF shield also blocks module's internal high frequency emissions from being radiated.

###

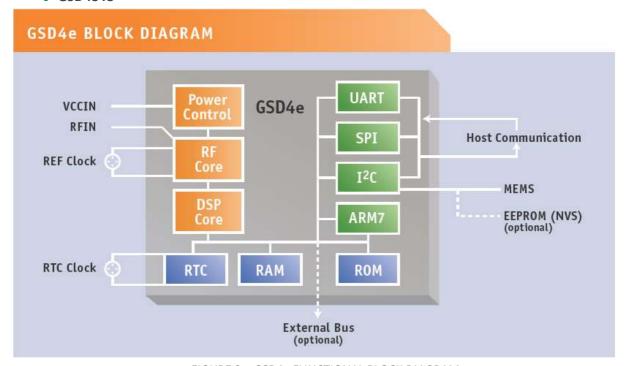

FIGURE 2 – GSD4e FUNCTIONAL BLOCK DIAGRAM

SiRFstarIV™ GSD4e is a navigation processor built on a low-power RF CMOS single-die, incorporating the baseband, integrated navigation solution software, ARM7 processor that form a complete stand alone or assisted-GPS engine.

SiRFstarIV<sup>™</sup> GSD4e GPS processor includes the following units:

- → GPS RF core incorporating LNA, down converter, fractional-N synthesizer and ADC block with selectable 2 and 4-bit quantization

- **→** GPS DSP core incorporating more than twice the clock speed and more than double the RAM capacity relative to predecessor market benchmarking SiRFStarIII<sup>™</sup> GPS processor

- → ARM7 microprocessor system incorporating 109MHz CPU and interrupt controller

- **★** ROM block as code storage for PVT applications

- ➡ RAM block for data cache

- ➡ RTC block

- **★** UART block

- → SPI block

- → Power control block for internal voltage domains management

### 11.3. APPLICATIONS

The ORG14XX series GPS antenna modules were specially designed to meet wide range of OEM configurations and applications.

### **ORG1400**

The ORG1400 is low profile GPS antenna module.

The ORG1400 is ideal for portable electronics applications with direct satellite visibility:

- + Handheld consumer navigation and multifunction devices

- ➡ Precise timing devices

- ★ Micro robots and micro UAVs

- → People and animal tracking systems

### **ORG1415**

The ORG1415 is standard version of the ORG14XX series GPS antenna modules.

The ORG1415 is ideal for standard positioning and navigation applications including indoor tracking:

- → People and animal tracking systems

- → Sports and recreation accessories

- → Vehicle tracking and fleet management systems

- → Workforce management systems

- → Automotive navigation systems

- Rescue and emergency systems

- → Marine navigation systems

### **ORG1418**

The ORG1418 is enhanced sensitivity version of the ORG1415 GPS antenna module.

The ORG1418 is ideal for applications where module installation position and orientation limits satellite visibility:

- → Automotive security systems

- Asset tracking SKU systems

- ★ Telemetric systems

- → Industrial navigation systems

### 12. ELECTRICAL SPECIFICATIONS

### 12.1. ABSOLUTE MAXIMUM RATINGS

Absolute Maximum Ratings are stress ratings only.

Stresses exceeding Absolute Maximum Ratings may damage the device.

|                            | Parameter                   |        |      |      | Units |

|----------------------------|-----------------------------|--------|------|------|-------|

| Dower Supply Voltage       | Basic series                | VCC    | -    | 2.2  | V     |

| Power Supply Voltage       | Standard and Premium series | VCC    |      | 6.5  | V     |

| TX Buffer Supply Voltage   |                             | VTX    | -    | 5.5  | V     |

| TX Buffer Source/Sink Curr | ent                         | ITX    | -10  | 10   | mA    |

| I/O Voltage                |                             | VIO    | -0.3 | 3.6  | V     |

| I/O Source/Sink Current    |                             | IIO    | -2   | +2   | mA    |

| 1.8V Source Current        |                             | I1V8   |      | 10   | mA    |

| ESD Rating                 |                             | V(ESD) | -2   | 2    | kV    |

| Power Dissipation          |                             | PD     | -    | 200  | mW    |

| Storage Temperature        |                             | TST    | -55  | +125 | °C    |

| Lead Temperature (10 sec.  | @ 1mm from case)            | TLEAD  |      | +260 | °C    |

TABLE 3 – ABSOLUTE MAXIMUM RATING

### 12.2. RECOMMENDED OPERATING CONDITIONS

Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.

|                          | Standard and Premium Series |               |                                             |      |      |      |       |

|--------------------------|-----------------------------|---------------|---------------------------------------------|------|------|------|-------|

| Parameter                | Symbo                       | Mode / Pad    | Test Conditions                             | Min  | Тур  | Max  | Units |

|                          |                             |               |                                             | 2.0  | 3.3  | 6.0  | V     |

| Power Supply Voltage     | VCC                         | VCC           | VCC falling                                 |      | 1.8  | 1.9  | V     |

|                          |                             |               | VCC rising                                  |      | 1.9  | 2.0  | V     |

|                          |                             | Acquisition   |                                             |      | 33   | 43   | mA    |

|                          | ICC                         | Tracking      | 130dBm (Outdoor)<br>VCC = 2V<br>TAMB = 25°C | 7    |      | 33   | mA    |

| Power Supply Current     |                             | CPU only1     |                                             |      | 14   |      | mA    |

| rower supply current     |                             | Standby1      |                                             |      | 0.1  |      | mA    |

|                          |                             | Hibernate     |                                             |      | 30   | 100  | μΑ    |

|                          |                             | Shutdown      |                                             |      | 0.5  | 1    | μΑ    |

| 1.8V Output Voltage      | V1V8                        | V1V8          |                                             | 1.77 | 1.80 | 1.83 | V     |

| 1.8V Output Current      | I1V8                        | V1V8          |                                             |      |      | 20   | mA    |

| TX Buffer Supply Voltage | VTX                         | VTX           |                                             | 1.80 |      | 5    | V     |

| TX Buffer Supply Current | ITX                         | VTX           |                                             |      | 1    | 10   | mA    |

| Input Voltage Low State  | VIL                         | UART/SPI/GPIO |                                             |      |      | 0.45 | V     |

|                                                   |            | ON_OFF          |                   |          |      | 0.3  | V  |

|---------------------------------------------------|------------|-----------------|-------------------|----------|------|------|----|

| Input Voltage Low State Input Voltage High State  | VIL<br>VIH | EN              |                   |          |      | 0.6  | V  |

| input voitage riigii state                        | VIII       | UART/SPI/GPIO   |                   | 1.26     |      | 3.6  | V  |

|                                                   |            | ON_OFF          |                   | 1.0      |      | 3.6  | V  |

| Input Voltage High State Output Voltage Low State | VIH<br>VOL | EN              |                   | 0.8      |      | VCC  | V  |

| Output voitage Low State                          | VOL        | UART            | IOL = 4mA         |          |      | 0.4  | V  |

| Output Voltage Low State                          | VOL        | SPI / GPIO      | IOL = 4mA         |          |      | 0.4  | V  |

| Output Voltage High State                         | VOH        | UART            | IOH = -4mA        | VTX -0.4 |      |      | V  |

| Output Voltage High State                         | VOH        | SPI / GPIO      | IOH = -4mA        | 1.35     | 1.71 | 1.8  | V  |

| Input Leakage Current                             | IIN(leak   | UART/SPI/GPIO T | VIN = 1.8V or 0V  | -10      |      | +10  | μΑ |

|                                                   | IIN(leak   | ON_OFF          | VIN = 1.8V or 0V  | -0.2     |      | +0.2 | μΑ |

| Input Leakage Current Input Capacitance           | )          | EN              | VIN = VCC or 0V   | -0.5     | 0.01 | 0.5  | μΑ |

| input capacitance                                 | CIN        | UART            |                   |          | 4    | 10   | pF |

| Input Capacitance                                 | CIN        | SPI / GPIO      |                   |          | 5    |      | pF |

| Operating Temperature3                            | TAMB       |                 |                   | -40      | +25  | +85  | °C |

| Relative Humidity                                 | RH         |                 | -40°C ≤TAMB≤+85°C | 5        |      | 95   | %  |

|                                                   |            |                 |                   |          |      |      |    |

TABLE 4 – STANDARD AND PREMIUM SERIES OPERATING CONDITIONS

|                                                   |           | Basi           | c series          |          |       |      |       |   |

|---------------------------------------------------|-----------|----------------|-------------------|----------|-------|------|-------|---|

| Parameter                                         | Symbol    | Mode / Pad     | Test Conditions   | Min      | Тур   | Max  | Units |   |

| Power supply voltage                              | VCC       | VCC            |                   | 1.71     | 1.80  | 1.89 | V     |   |

|                                                   |           | Acquisition    |                   |          | 33    | 43   | mA    |   |

|                                                   |           | Tracking       |                   | 7        |       | 33   | mA    |   |

| Power Supply Current                              | ICC       | CPU only1      | -130dBm (Outdoor) |          | 14    |      | mA    |   |

| Power Supply Current                              | icc       | Standby1       | TAMB = 25°C       |          | 0.1   |      | mA    |   |

|                                                   |           | Hibernate      |                   |          | 20    | 30   | μΑ    |   |

|                                                   |           | Shutdown       |                   | Not      |       |      |       |   |

| 1.8V Output Voltage                               | V1V8      | V1V8           |                   |          |       |      | •     | V |

| Input Voltage Low State                           | VIL       | UART/SPI/GPIO  |                   |          |       | 0.45 | V     |   |

|                                                   |           | ON_OFF         |                   |          |       | 0.45 | V     |   |

| Input Voltage Low State Input Voltage High State  | VIL       | EN             |                   | Not      |       |      |       |   |

| input voitage riigh state                         | VIII      | UART/SPI/GPIO  |                   |          | 0.70• | VCC  |       |   |

|                                                   |           | ON_OFF         |                   | 0.70•VCC |       | 3.6  | V     |   |

| Input Voltage High State Output Voltage Low State | VIH       | EN             |                   | Not      |       |      |       |   |

| Output voltage Low State                          | VOL       | UART/SPI/GPIO  | IOL = 4mA         |          |       |      |       |   |

| Output Voltage High State                         | VOH       | UART/SPI/GPIO  | IOH = -4mA        | 0.75•VCC |       |      | V     |   |

| Input Leakage Current                             | IIN(leak) | All input pads | VIN = 1.8V or 0V  | -10      |       | +10  | μΑ    |   |

| Input Capacitance                                 | CIN       | All input pads |                   |          | 5     |      | pF    |   |

| Operating Temperature3 | TAMB |                   | -40 | +25 | +85 | °C |

|------------------------|------|-------------------|-----|-----|-----|----|

| Relative Humidity      | RH   | -40°C ≤TAMB≤+85°C | 5   |     | 95  | %  |

TABLE 5 - BASIC SERIES OPERATING CONDITIONS

### Notes:

- 1. Transitional states of ATP™ low power mode

- 3 Operation below -20°C to -40°C and above +70°C to +85°C is accepted, but TTFF may increase

### 13. PERFORMANCE

### **13.1. ACQUISITION TIMES**

TTFF (Time To First Fix) – is the period of time from GPS power-up till position estimation.

### **Hot Start**

A hot start results from software reset after a period of continuous navigation or a return from a short idle period that was preceded by a period of continuous navigation.

In this state, all of the critical data (position, velocity, time, and satellite ephemeris) is valid to the specified accuracy and available in RAM.

### **Warm Start**

A warm start typically results from user-supplied position and time initialization data or continuous RTC operation with an accurate last known position available in memory.

In this state, position and time data are present and valid, but ephemeris data validity has expired.

### **Cold Start**

A cold start acquisition results when either position or time data is unknown.

### **Aided Start**

Aiding is a method of effectively reducing the TTFF by making every start Hot or Warm.

|                      | TTFF  | Test Condition  | Signal Level |

|----------------------|-------|-----------------|--------------|

| Hot Start            | < 1s  |                 |              |

| Aided Start1         | < 10s |                 |              |

| Warm Start           | < 32s | Outdoor, Static | -130 dBm     |

| Cold Start           | < 35s |                 |              |

| Signal Reacquisition | < 1s  |                 |              |

TABLE 6 - ACQUISITION TIMES

### 13.2. SENSITIVITY

| Test Condition | Signal Level              |

|----------------|---------------------------|

| Tracking       | -163 dBm                  |

| Navigation     | -161 dBm (Deep<br>Indoor) |

| Aided1         | -156 dBm                  |

| Cold Start     | -148 dBm                  |

TABLE 7 - SENSITIVITY

### **13.3. RECEIVED SIGNAL STRENGTHS**

|               | ORG1400  | ORG1415  | ORG1418  |  |

|---------------|----------|----------|----------|--|

| Average C/N02 | 40 dB-Hz | 45 dB-Hz | 48 dB-Hz |  |

### TABLE 8 – RECEIVED SIGNAL STRENGTH

### Notes:

- 1. Host-assisted device by SGEE™ or self-assisted by CGEE™ or Ephemeris Push

- 2. Averaging of 5 SV's with highest C/N0 @ -130dBm, HDOP <1.5

### **13.4. POWER CONSUMPTION**

| Standard and Premium series |                   |  |

|-----------------------------|-------------------|--|

| Operation Mode              | Power Consumption |  |

| Acquisition                 | 80mW              |  |

| Tracking                    | 20-75mW           |  |

| Hibernate                   | 80μW              |  |

TABLE 9 – STANDARD AND PREMIUM SERIES POWER CONSUMPTION @ Vcc = 2V (AVERAGE)

| Basic series   |                   |  |

|----------------|-------------------|--|

| Operation Mode | Power Consumption |  |

| Acquisition    | 100mW             |  |

| Tracking       | 10-70mW           |  |

| Hibernate      | 40μW              |  |

TABLE 10 – BASIC SERIES POWER CONSUMPTION @ Vcc = 1.8V (AVERAGE)

### 13.5. ACCURACY

|          |             |             | Accuracy    | Units | Test Conditions                  |

|----------|-------------|-------------|-------------|-------|----------------------------------|

|          |             | CEP (50%)   | < 2.5       | m     | -130 dBm (Outdoor), Static       |

|          | Horizontal  |             | < 2         | m     | -130 dBm (Outdoor), SBAS, Static |

|          | попідопітаї | 2dRMS (95%) | < 5         | m     | -130 dBm (Outdoor), Static       |

| Position |             | 20NN3 (93%) | < 4         | m     | -130 dBm (Outdoor), SBAS, Static |

| POSITION | Vertical    | VEP (50%)   | < 4         | m     | -130 dBm (Outdoor), Static       |

|          |             |             | < 3         | m     | -130 dBm (Outdoor), SBAS, Static |

|          |             |             | 2dDMS (0E%) | <7.5  | m                                |

|          |             | 2dRMS (95%) | < 6         | m     | -130 dBm (Outdoor), SBAS, Static |

| Velocity | Horizontal  | 50%         | < 0.01      | m/s   | -130 dBm (Outdoor), 30 m/s       |

| Heading  |             | 50%         | < 0.01      | 0     | -130 dBm (Outdoor), 30 m/s       |

| Ti       | me          | 1 PPS       | < 1         | μs    | -130 dBm (Outdoor)               |

TABLE 11 – ACCURACY

### **13.6. DYNAMIC CONSTRAINS**

| Velocity <     | 515 m/s 1,000 knots |            |

|----------------|---------------------|------------|

| Acceleration < | 4                   | æ          |

| Altitude <     | 18,288 m            | 60,000 ft. |

TABLE 12 – DYNAMIC CONSTRAINS

Note: 1. Standard dynamic constrains according to regulatory limitations

### 14. POWER MANAGEMENT

### **14.1. POWER STATES**

### Full Power state (Acquisition/Tracking)

The module stays in full power until a position solution is made and estimated to be reliable.

During the acquisition, processing is more intense than during tracking, thus consuming more power.

### **CPU Only state**

This is the state when the RF and DSP sections are partially powered off.

The state is entered when the satellites measurements have been acquired but the navigation solution still needs to be computed.

### Standby state

This is the state when the RF and DSP sections are completely powered off and baseband clock is stopped.

### Hibernate state

In this state the RF, DSP and baseband sections are completely powered off leaving only the RTC and Battery-Backed RAM running.

The module will perform Hot Start if held in Hibernate state less than 2 hours after valid position solution was acquired.

### Shutdown state

In this state the ORG14XX series module is inhibited by driving EN input low.

The module will perform Cold Start after Shutdown state.

### **14.2. POWER SAVING MODES**

The ORG14XX series module has three power management modes available in modules with Basic firmware – ATP™, APM™ and PTF™, which are controlled by internal state machine. These modes provide different levels of power saving with different degradation level of position accuracy.

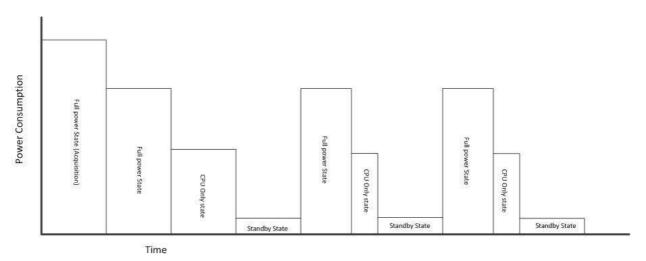

### Adaptive Trickle Power (ATP™)

Adaptive Trickle Power (ATP $^{TM}$ ) is best suited for applications that require navigation solutions at a fixed rate as well as low power consumption and an ability to track weak signals.

This power saving mode provides the most accurate position.

In ATP™ mode the ORG14XX module is intelligently cycled between Full Power, CPU Only and Standby states to optimize low power operation.

FIGURE 3 - ATP™ TIMING

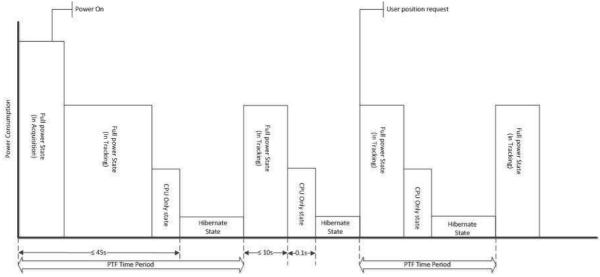

### Push-to-Fix (PTF™)

Push-to-Fix (PTF™) is best suited for applications that require infrequent navigation solutions, optimizing battery life time.

In PTF™ mode the ORG14XX module is mostly in Hibernate state, waked up for Ephemeris and Almanac refresh in fixed periods of time.

The PTF™ period is 30 minutes by default but can be anywhere between 10 seconds and 2 hours. When the PTF mode is enabled the receiver will stay in Full Power state until the good navigation solution is computed.

When the application needs a position report it can toggle the ON\_OFF pad to wake up the module. In this case, a new PTF™ cycle with default settings begins.

FIGURE 4 – PTF™ TIMING

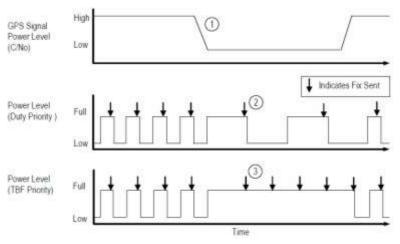

### Advanced Power Management (APM™)

Advanced Power Management (APM™) is designed for aided GPS applications.

Advanced Power Management (APM $^{\text{TM}}$ ) is designed to give the user more options to configure the power management. The APM $^{\text{TM}}$  mode allows power savings while ensuring that the Quality of the Solution (QoS) in maintained when signals level drop.

In addition to setting the position report interval, a QoS specification is available that sets allowable error estimates and selects priorities between position report interval and more power saving. The user may select between Duty Cycle Priority for more power saving and TBF (Time Between Fixes) Priority with defined or undefined maximum horizontal error.

TBF range is from 10 to 180 sec. between fixes, Power Duty Cycle range is between 5 to 100%. Maximum position error is configurable between 1 to 160m.

The number of APM™ fixes is configurable up to 255 or set to continuous.

In APM™ mode the module is intelligently cycled between Full Power and Hibernate states.

FIGURE 5 - APM™ TIMING

- 1.GPS signal level drops (e.g. user walks indoors)

- 2. Lower signal results in longer ON time. To maintain Duty Cucle, OFF time is increased.

- 3. Lower signal means missed fix. To maintain future TBFs, the module goes info Full Power state until signal levels improve.

### 15. EXTENDED FEATURES

### 15.1. ALMANAC BASED POSITIONING (ABP™)1

With ABP™ mode enabled, the user can get shorter Cold Start TTFF as a tradeoff with the position error.

When no sufficient Ephemeris data is available to calculate an accurate solution, a coarse solution will be provided where the position is calculated based on one or more of the SVs having their states derived from Almanac data.

Almanac data for ABP™ purposes may be stored factory set, broadcasted or pushed.

### 15.2. ACTIVE JAMMER REMOVER

Jamming Remover is an embedded DSP block that detects, tracks and removes up to 8 Continuous Wave (CW) type signals of up to 80dB-Hz each.

Jamming Remover is effective only against continuous narrow band interference signals and covers GPS L1 1575Mhz frequency ±4MHz.

**15.3. CLIENT GENERATED EXTENDED EPHEMERIS (CGEE™)**

The CGEE™ feature allows shorter TTFF by providing predicted (synthetic) ephemeris files created within a lost host system from previously received broadcast Ephemeris.

The prediction process requires good receipt of broadcast Ephemeris data for all satellites.

EE files created this way are good for up to 3 days and then expire.

The CGEE™ feature requires avoidance of power supply removal.

CGEE™ data files are stored on internal or external EEPROM or Serial Flash and managed by the receiver or storage and management is done by host.

### Note:

1. Not available in modules with Standard firmware

### 16. INTERFACE

### **16.1. PAD ASSIGNMENTS**

TABLE 13 - ORG14XX PIN-OUT

| Pad Number | Pad Name | Pad Description             | Direction | Default | Notes                                  |  |

|------------|----------|-----------------------------|-----------|---------|----------------------------------------|--|

| 1          | RX       | UART Receive                | Input     | High    | 1.8 – 3.6V                             |  |

| 2          | TX       | UART Transmit               | Output    | High    | High state voltage level is set by VTX |  |

| 3          | VTX      | TX Buffer Power             | Power     |         | 1.8 – 5.0V                             |  |

| 4          | SCK      | SPI Clock                   | Input     | Low     |                                        |  |

| 5          | nSE      | SPI Chip Select             | Input     | High    | 1.8 – 3.6V                             |  |

| 6          | SDO      | SPI Data Out                | Output    | High    |                                        |  |

| 7          | EN       | Module Enable               | Input     | High    | Drive low to inhibit the module        |  |

| 8          | VCC      | System Power                | Power     |         | 2 - 6V                                 |  |

| 9          | V1V8     | 1.8V Source                 | Power     |         | Voltage source. Do not power this pad. |  |

| 10         | GND      | System Ground               | Power     |         |                                        |  |

| 11         | GND      | System Ground               | Power     |         |                                        |  |

| 12         | GND      | System Ground               | Power     |         |                                        |  |

| 13         | GND      | System Ground               | Power     |         |                                        |  |

| 14         | GND      | System Ground               | Power     |         |                                        |  |

| 15         | WAKEUP   | Power Status                | Output    | Low     | 1.8V compatible                        |  |

| 16         | nRESET   | Asynchronous Reset          | Input     | High    | Do not drive                           |  |

| 17         | ON_OFF   | Power State Control         | Input     | Low     | 1.8 – 3.6V                             |  |

| 18         | DR_SDA   | Master I <sup>2</sup> C SDA | Bi-dir    | High    | 1.01/ sampatible                       |  |

| 19         | DR_SCL   | Master I <sup>2</sup> C SCL | Output    | High    | 1.8V compatible                        |  |

| 20         | EIT      | External Interrupt          | Input     | High    | 1.8 – 3.6V                             |  |

| 21         | 1PPS     | UTC Time Mark               | Output    | Low     | 1.8V compatible                        |  |

| 22         | SDI      | SPI Data In                 | Input     | High    | 1.8 – 3.6V                             |  |

### **16.2. CONNECTIVITY**

### **16.2.1. POWER**

The ORG14XX series module requires only one power supply VCC, which can be supplied directly from a battery since the module has internal regulators.

Power supply current consumption varies according to the processor load and satellite acquisition.

It is recommended to keep the power supply on all the time in order to maintain the non-volatile RTC and RAM active for fastest possible TTFF. When the VCC is powered off settings are reset to factory default and the receiver performs Cold Start on next power up.

### Power supply - Basic series

In Basic series the VCC is 1.8V DC.

Typical ICC current is 37mA during acquisition. Peak ICC current is 60mA.

Typical ICC current in Hibernate state is 20μA.

Voltage ripple below 50mVPP allowed for frequency between 100KHz to 1MHz.

Voltage ripple below 15mVPP allowed for frequency above 1MHz.

Higher voltage ripple may compromise the ORG14XX series module performance.

### Power supply – Standard and Premium series

In Standard and Premium series VCC range is 2 to 6V DC.

Typical ICC current is 23mA during acquisition. Peak ICC current is 50mA.

Typical ICC current in Hibernate state is 50μA.

Voltage ripple below 30mVPP allowed for frequency above 1MHz.

Higher voltage ripple may compromise the ORG14XX series module performance.

In Standard and Premium series the under voltage lockout (UVLO) circuit prevents the device from misoperation at low input voltages.

The UVLO circuit prevents the integrated DC-DC switch-mode regulator from turning on the switch or rectifier MOSFET under undefined conditions. It has a UVLO threshold set to 1.8V. Fully functional operation is permitted for input voltage down to the falling UVLO threshold level. The converter starts operation again once the input voltage trips the rising UVLO threshold level.

### TX power

VTX power input is for integrated data output level shifter between 1.8V GPS processor domain and host.

VTX power supply range is 1.8 to 3.6V DC according to required TX output voltage swing. Typical ITX current is 1mA and varies with input load of host.

VTX may be externally connected to VCC, while module and host I/O are in same voltage domain.

VTX may be externally connected to V1V8, while host I/O is in 1.8V voltage domain. Data output level shifter is internally controlled by GPS processor and automatically turned off during low power states.

### 1.8V power source

V1V8 power supply provides regulated 1.8V voltage source for peripheral components, like MEMS sensors connected to DR  $I^2C$  bus.

Maximum I1V8 continuous output current is 20mA.

### **Ground**

Single Ground pad should be connected to host PCB Ground with shortest possible trace or via.

### 16.2.2. HOST CONTROL INTERFACE

### **ON OFF input**

The ON OFF control input is used to switch the receiver between different power states.

- If the system is in Hibernate state, an ON\_OFF pulse will move to Full Power mode

- **•** If the system is in ATP™ mode, an ON\_OFF pulse will move it to Full Power mode.

- **†** If the system is in PTF™ mode, an ON OFF pulse will initiate one PTF™ cycle.

- if the system is already in Full Power mode, an ON OFF pulse will initiate orderly shutdown.

ON\_OFF pulse requires a rising edge and high level that persists for at least  $100\mu s$  in order to be detected. Resetting the ON\_OFF detector requires that ON\_OFF go to logic low at least  $100\mu s$ . Recommended low-high-low pulse length is 100ms.

ON\_OFF interrupts with less than 1 sec intervals are not recommended.

Multiple switch bounce pulses are recommended to be filtered out.

FIGURE 7 - RECOMMEND ON\_OFF TIMING

ON\_OFF input has internal pull-down resistor of  $100k\Omega$ .

ON\_OFF pulse high state is 1.2 to 6V. Do not drive high permanently or pull-up this input. Must be connected to host.

### **WAKEUP** output

The WAKEUP pad is an output from the ORG14XX series module, used to flag for power state. A logic low on this output indicates that the module is in one of its low-power states - Hibernate or Standby. A logic high on this output indicates that the module is in Full Power state. In addition WAKEUP output can be used to control enable of auxiliary devices. Wakeup output is LVCMOS 1.8V compatible. Do not connect if not in use.

### **Enable input**

The Enable control input can be used to fully inhibit the ORG14XX module. Enable signal is active low and has internal  $100k\Omega$  pull-up resistor. Do not connect to this input if the feature is not in use.

### nRESET input

The Power-on-Reset (POR) is generated internally in the ORG14XX series module.

Additionally, manual reset option is available through nRESET pad.

Resetting the module clears the RTC block and configuration settings become default.

nRESET signal should be applied for at least 1µs.

nRESET input is active low and has internal pull-up resistor of  $86k\Omega$ .

Do not drive this input high. Do not connect if not in use.

1PPS output

The pulse-per-second (PPS) output provides a pulse signal for timing purposes.

Pulse length (high state) is 200ms about 1µs synchronized to full UTC second.

The UTC time message is generated and put into output FIFO 300ms after PPS.

The exact time between the PPS and UTC time message delivery depends on message rate, message queue and communication baud rate.

1PPS output is LVCMOS 1.8V compatible. Do not connect if not in use.

### 16.2.3. HOST DATA INTERFACE

The ORG14XX series module has 2 types of interface ports to connect to host: UART and SPI. The ORG14XX series module is factory set to support UART or SPI by internal configuration straps.

### **UART**

The module has a 4-wire UART port:

- TX used for GPS data reports. Output logic high voltage level is set by VTX.

- **★** RX used for receiver control. Input logic high voltage level is 1.45 to 3.6V.

- → nCTS is optionally used for hardware flow control.

- ➡ High when host allows TX from the module. Input logic high voltage level is 1.45 to 3.6V.

- nRTS is optionally used for hardware flow control.

- ➡ High when module is ready to TX. Output logic high voltage level is 1.8V.

Operation:

The UART performs bit-by-bit transmitting and receiving in 8-bit octets when module is active. On the transmit side 1 start bit, 8 data bits and 2 stop bits followed by next character or idle

Designers should treat computations of maximum message output capacity from ORG14XX with 11-bits per transmitted character.

On the receive side 1 start bit, 8 data bits, 1 stop bit or longer is accepted.

FIGURE 8 - UART INTEGRITY

Because UART transmission is asynchronous and sampled by the receiver, both sides require closely match bit-rate clocks, and that data bit waveform and timing distortion at the receiver should be limited.

The default protocol is NMEA@4,800bps.

The configuration for baud rates and respective protocols can be changed by commands via NMEA or OSP™ protocols.

| Baud Rate (bps) | Error (%) |

|-----------------|-----------|

| 4800            | 0.06      |

| 9600            | 0.00      |

| 19200           | 0.00      |

| 38400           | 0.07      |

| Baud Rate (bps) | Error (%) |

|-----------------|-----------|

| 115200          | 0.24      |

| 230400          | 1.04      |

| 460800          | 0.60      |

| 921600          | 2.40      |

TABLE 14 – UART BAUD RATE TOLERANCE

Maximum allowed clock rate difference between ORG14XX and host is 2.0% overall. Maximum bit-edge distortion  $\leq$  5% bit length. Maximum bit jitter  $\leq$  5% bit length.

### SP

The SPI (Serial to Peripheral Interface) is a master/slave synchronous serial bus that consists of 4 signals:

- ★ Serial Clock (SCK) from master to slave.

- → Serial Data Out (also called Master Out Slave In or MOSI) from master.

- → Serial Data In (also called Master In Slave Out or MISO) from slave.

- + Chip Select (CS) from master.

The host interface SPI of the ORG14XX series module is a slave mode SPI.

The four SPI pads are RX (MOSI), TX (MISO), nRTS(nCS) and nCTS(SCK).

Output logic high voltage level is set by VTX. Inputs are 3.6V tolerant.

The host interface SPI features are:

- TX and RX each have independent 1024 byte FIFO buffers.

- → RX and TX have independent, software specified two byte idle patterns of '0xA7 0xB4'.

- TX FIFO is disabled when empty and transmits its idle pattern until re-enabled.

- RX FIFO detects a software specified number of idle pattern repeats and then disables FIFO input until the idle pattern is broken.

- **†** FIFO buffers can generate an interrupt at any fill level.

- **★** SPI detects synchronization errors and can be reset by software.

- **★** Supports a maximum clock of 6.8MHz.

- → Default GPS data output format is NMEA standard.

FIGURE 9 - SPI TIMING

| Symbol | Parameter           | Min | Max | Units |

|--------|---------------------|-----|-----|-------|

| tCLK   | SCK Time Period     | 140 |     | ns    |

| tCSS   | nCS Setup Time      | 0.5 | 1   | tCLK  |

| tCS    | nCS High Time       | 1   |     | tCLK  |

| tWH    | SCK High Time       | 0.5 |     | tCLK  |

| tWL    | SCK Low Time        | 0.5 |     | tCLK  |

| tCSH   | nCS Hold Time       | 0.5 | 1   | tCLK  |

| tSU    | Data In Setup Time  | 0.5 |     | tCLK  |

| tH     | Data In Hold Time   | 0.5 |     | tCLK  |

| tV     | Output Valid        | 0.5 |     | tCLK  |

| tHO    | Output Hold Time    | 0.5 |     | tCLK  |

| tDIS   | Output Disable Time |     | 0.5 | tCLK  |

TABLE 15 - SPI TIMING

### Operation:

The SPI performs bit-by-bit transmitting and receiving at the same time whenever nCS is asserted and SCK is active. In order to communicate properly with SPI device, the protocol must be agreed – specifically- SPI mode and an idle byte pattern.

Among 4 SPI modes of the clock polarity (CPOL) and clock phase (CPHA) only SPI Mode 1 <CPOL="0", CPHA ="1"> is currently supported:

- → At CPOL="0" the base value of the clock is zero.

- → For CPHA="1", data are read on the clock's falling edge and data are changed on a rising edge.

On power up, the first message to come out of the module is the "OK\_TO\_SEND" message. It takes about 20ms from power up for the module SPI drivers to get initialized.

The slave has no way of forcing data to the master to indicate it is ready for transmission - the master must poll the client periodically.

Since the specified idle 2-byte pattern for both receive and transmit is '0xA7 0xB4', the master can transmit this idle pattern into the slave repeatedly. If the master receives idle patterns back from the slave, it indicates that the slave currently has nothing to transmit but is ready to communicate.

On the module receive side, the host is expected to transmit idle pattern when it is querying the module's transmit buffer. In this way, the volume of discarded bytes is kept nearly as low as in the UART implementation because the module hardware does not place most idle pattern bytes in its RX FIFO. Most messaging can be serviced with polling. The FIFO thresholds are placed to detect large messages requiring interrupt-driven servicing.

On the module transmit side the intent is to fill the FIFO only when it is disabled and empty. In this condition, the module's SPI driver software loads as many queued messages as can completely fit in the FIFO. Then the FIFO is enabled.

The host is required to poll messages until idle pattern bytes are detected.

At this point the module's FIFO is empty and disabled, allowing the module's SPI driver to again respond to an empty FIFO interrupt and load the FIFO with any messages in queue. Notes:

For SPI communication, read and write operations both require data being sent to the Slave SPI (idle bytes for reads and message data for writes). Any time data is sent to the module via the SPI bus, the Slave SPI of the module will send an equal amount of data back to the host.

These bytes must be buffered either in hardware or software, and it is up to the host to determine if the bytes received may be safely discarded (idle bytes), or should be passed on to the application handling GPS communication. Failure to properly handle data received from the SPI slave can result in corrupted GPS messages.

The external SPI master may send idle bytes and complete messages in a single transmission, provided that idle bytes shall not be inserted inside of a message.

The idle byte pattern and repeat count prevents the problem of messages lost due to normal occurrence of idle byte patterns within message data with high probability.

The external SPI master shall not send partial messages.

All transmissions from the SPI master shall be in multiples of 8 bits.

The external SPI master shall transmit the idle byte pattern when reading the SPI slave's transmit buffer when the master has no message data to transmit.

The SPI slave shall be serviced at a rate that will keep the TX FIFO empty.

### 16.2.4. SMART SENSORS DATA INTERFACE

The ORG14XX module master mode I<sup>2</sup>C interface provides optional support for Dead Reckoning (DR) and optional code patch upload.

This bus has 2 lines, DR\_SCL and DR\_SDA, both are pseudo open-drain and require external pull-up resistors. Discrete EIT input is optionally used to wake up the module from Hibernate state.

### Dead Reckoning (DR) I<sup>2</sup>C Interface

The DR  $I^2C$  interface supports required sensor instruments for dead reckoning applications such as gyros, accelerometers, compasses or other sensors that can operate with an  $I^2C$  bus.

The ORG14XX module acts as the I<sup>2</sup>C Master and the sensor devices function in Slave mode.

This provides a very low latency data pipe for the critical sensor data so that it can be used in the Navigation Library and Kalman filter to enhance navigation performance.

The MEMS algorithms perform a sensor data fusion with the GPS signal measurements. GPS measurements can be used to calibrate the MEMS sensors during periods of GPS navigation. The MEMS sensors can augment GPS measurements, and can be more accurate than GPS under degraded GPS signal conditions and certain dynamics.

DR I<sup>2</sup>C interface supports:

- **+** Common sensor formats

- ➡ Typical data lengths (command + in/data out) of several bytes

- **★** Standard I<sup>2</sup>C bus maximum data rate 400kbps

- Minimum data rate 100kbps

In current Premium firmware implementation, MEMS sensors integration provides a pseudo "position pinning" feature to prevent position wander and heading instability.

### **EIT input**

The EIT (External Interrupt) input is optionally used by external sensors to provide a discrete interrupt to the module when a change of state is detected.

The input is either a level triggered or an edge triggered programmable for high/ low level or rising/falling edge. The input is disabled during initial power-up or reset.

EIT interrupt input logic high state is 1.8 to 3.6V.

Do not connect to this input if the feature is not in use.

### **Data Storage Support**

The DR I<sup>2</sup>C interface is available at boot-up for uploading data from a serial EEPROM.

Firmware updates may be provided from time to time to address ROM firmware issues as a method of performance improvement.

The DR I<sup>2</sup>C interface also supports serial flash devices used to store ARM7TDMI patch loads, including optional:

- ➡ FIFO support

- → ARM7TDMI dedication to I<sup>2</sup>C interface during serial flash read or write

### 16.3. TYPICAL APPLICATION CIRCUIT

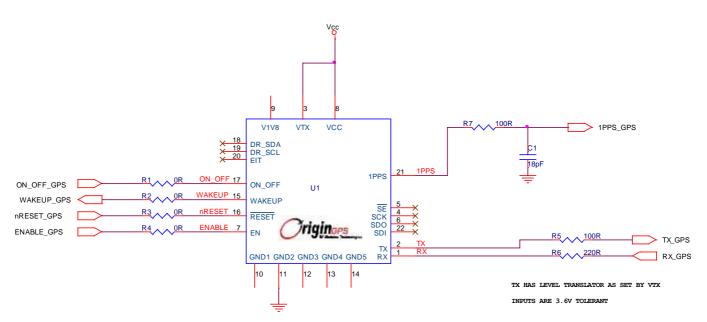

**UART Host Interface – ordering codes R01, R02**

FIGURE 10 - UART INTERFACE CIRCUIT

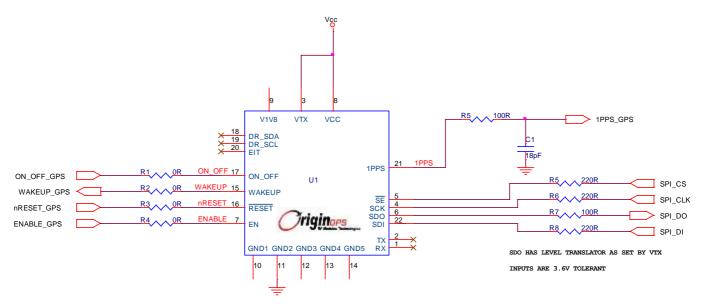

SPI Host Interface - ordering code R03

FIGURE 11 - SPI INTERFACE CIRCUIT

### 17. PCB LAYOUT

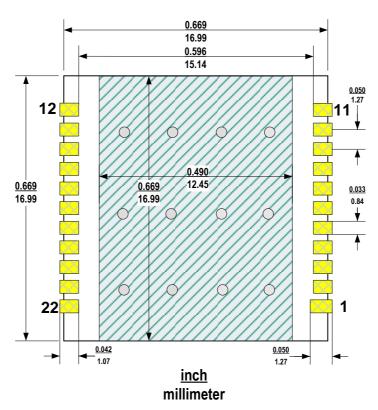

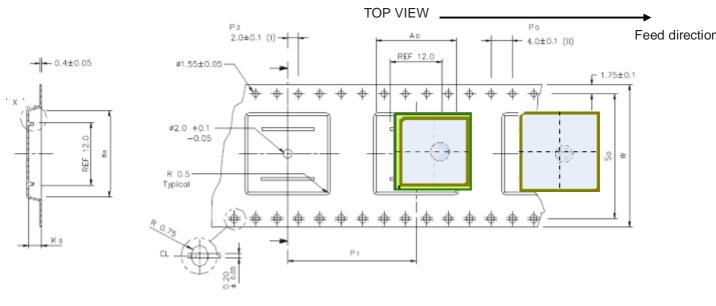

### 17.1. FOOTPRINT

### **TOP VIEW**

FIGURE 12 – FOOTPRINT

Ground pad at the middle should be connected to main Ground plane by multiple vias.

Ground pad at the middle should be solder masked.

Silk print of module's outline is highly recommended.

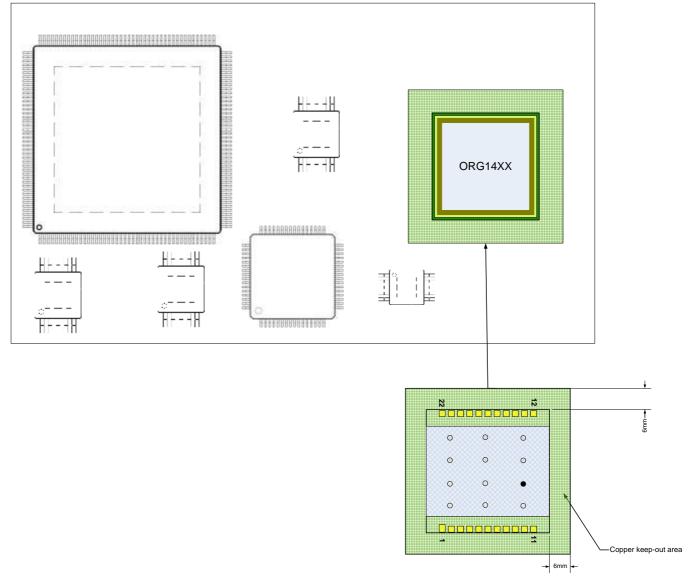

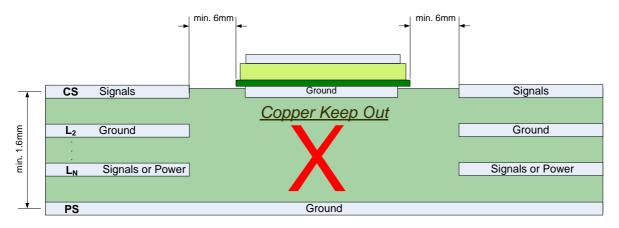

### 17.2. DESIGN RESTRICTIONS

Avoid current loops by connecting single Ground pad to main Ground.

Route the selected Ground pad to main Ground with shortest possible trace or via.

Avoid copper pour on the module side, keeping out the module minimum 6mm from the copper planes, metals planes or enclosures, connectors or LCD screens (Fig. 8-2).

Keep out of minimum 1.6mm from the copper planes under the ORG14XX GPS module (Fig. 8-3). Keep out of signal or switching power traces and vias under the ORG14XX GPS module.

Signal traces to/from ORG14XX GPS module should have minimum length.

In case of adjacent high speed components, like CPU or memory, high frequency components, like transmitters, clock resonators or oscillators, metal planes, like LCD or battery enclosures, please contact OriginGPS for more precise, application specific recommendations.

### 17.3. PLACEMENT

Special attention should be paid during GPS module placement and position on host PCB.

### 17.4. PCB STACK UP

FIGURE 14 – TYPICAL PCB STACK UP

### 18. OPERATION

When power is first applied, the ORG14XX series module goes into a Hibernate state while integrated RTC starts and internal FSM sequences though to "Ready-to-Start" state.

While in "Ready-to-Start" state, the module awaits a pulse to the ON\_OFF input.

The host is not required to control external master nRESET since module's internal reset circuitry handles detection of application of power.

### **18.1. STARTING THE MODULE**

Module start-up procedure depends upon the chosen ordering option.

|                             | <b>Boot Option 01</b> | <b>Boot Option 02</b> | <b>Boot Option 03</b> |

|-----------------------------|-----------------------|-----------------------|-----------------------|

| Ordering code               | ORG14XX-xx01          | ORG14XX-xx02          | ORG14XX-xx03          |

| Power On State              | Full Power            | Hibernate             | Hibernate             |

| Host Interface              | UART                  | UART                  | SPI                   |

| Interface settings on power | 4,800 bps 8-N-1       | 4,800 bps 8-N-1       | Slave                 |

| Data format on power        | NMEA                  | NMEA                  | NMEA                  |

TABLE 16 - HARDWARE OPTION

### 01 ordering code:

→ The module has integrated power-up circuit that automatically asserts ON\_OFF pulse 1 sec. after FSM indicates "Ready-to-Start" condition.

### 02 and 03 ordering codes:

- → A pulse on the ON\_OFF input will command the module to start.

- → Since integrated RTC startup times are variable, detection of when the module is ready to accept an ON\_OFF pulse requires the host to either wait for a fixed interval of 1 sec., or to monitor a pulse on module WAKEUP output that indicates FSM "Ready-to-Start".

- → Optionally, a pulse on the ON\_OFF input can be asserted every second until the module starts by indicating logic high level on WAKEUP output.

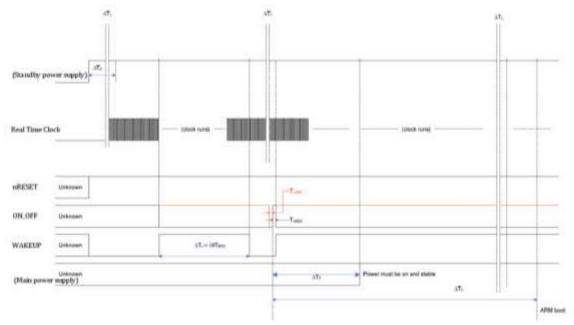

FIGURE 15 – STARTUP TIMING

| Symbol | Parameter                | Condition    | Min        | Тур        | Max        | Units |

|--------|--------------------------|--------------|------------|------------|------------|-------|

| fRTC   | RTC frequency            | 25°C         | -20 ppm    | 32768      | +20 ppm    | Hz    |

| tRTC   | RTC tick                 | 25°C         |            | 30.5176    |            | μs    |

| ΔΤ1    | RTC startup time         |              |            | 300        |            | ms    |

| ΔΤ0    | Power stabilization      |              | 6·tRTC+∆T1 | 7·tRTC+∆T1 | 8·tRTC+∆T1 | μs    |

| ΔΤ6    | WAKEUP pulse             | RTC running  |            | 10         |            | tRTC  |

| ΔTLOW  | ON_OFF low               |              | 3          |            |            | tRTC  |

| ΔTHIGH | ON_OFF high              |              | 3          |            |            | tRTC  |

| ΔΤ3    | Startup sequencing       | After ON_OFF |            | 1024       |            | tRTC  |

| -      | ON_OFF to WAKEUP high    | After ON_OFF |            | 6          |            | tRTC  |

| ΔΤ5    | ON_OFF to ARM start      | After ON_OFF |            | 2130       |            | tRTC  |

| ΔΤ7    | Main power source start1 | WAKEUP high  | 0          | 30         | 300        | tRTC  |

TABLE 17 - STARTUP TIMING

### Note:

1. When power provided through dual supply. Low quescent current power source (LDO) for Hibernate state, and high efficiency source (DC-DC) for Full Power state. The main power supply should be able to provide current for Full Power state within 1ms after WAKEUP is high.

### 18.2. VERYFING THE MODULE HAS STARTED

The ORG14XX module WAKEUP output will go logic high indicating the GPS processor has started. System activity indication depends upon the chosen ordering option.

01 and 02 ordering codes:

- ➡ When active, the module will output NMEA messages at the 4800bps.

- ➡ First NMEA message after power-up is '\$PSRF150,1\*3E'.

03 ordering code:

- → Since the module is SPI slave, there is no possible indication of system "ready" through SPI data interface.

- → The host must initiate SPI connection approximately 1 sec. after WAKEUP output goes high.

### 18.3. SHUTTING DOWN THE MODULE

Transferring the ORG14XX series module into Hibernate state can be initiated in two ways:

- ➡ By a pulse on the ON OFF input when the ORG14XX module in Full Power state.

- **+** By serial message MID205 (OSP™) or \$PSRF117 (NMEA).

- **★** Last message before Hibernate state is '\$PSRF150,1\*3F'.

The orderly shutdown may take anywhere from 10ms to 900ms to complete, depending upon operation in progress and messages pending, and hence is dependent upon serial interface speed and controls.

### 19. SOFTWARE FUNCTIONS

The module supports NMEA-0183 protocol and One Socket Protocol (OSP™).

### 19.1. NMEA

NMEA is generic ASCII protocol used by general purpose GNSS receivers.

### **NMEA Output Messages**

| Message        | Description                                                                           |

|----------------|---------------------------------------------------------------------------------------|

| \$GPGGA        | Time, position and fix type data                                                      |

| \$GPGLL1       | Latitude, longitude, UTC time of position fix and status                              |

| \$GPGSA        | GPS receiver operating mode, satellites used in the position solution and DOP values  |

| \$GPGSV        | The number of GPS satellites in view, satellite ID, elevation, azimuth and SNR values |

| \$GPRMC        | Time, date, position, course and speed data                                           |

| \$GPVTG1       | Course and speed information relative to the ground                                   |

| \$GPZDA1       | 1PPS timing message                                                                   |

| \$PSRF150      | OK to send data to the module                                                         |

| \$PSRF155      | Extended Ephemeris Proprietary Message                                                |

| \$PSRF156,0x20 | ECLM ACK/NACK                                                                         |

| \$PSRF156,0x21 | ECLM EE Get Age response                                                              |

| \$PSRF156,0x22 | ECLM Get SGEE Age response                                                            |

| \$PSRF156,0x23 | ECLM Download Initiate Request                                                        |

| \$PSRF156,0x24 | ECLM Erase Storage File                                                               |

| \$PSRF156,0x25 | ECLM Update File Content                                                              |

| \$PSRF156,0x26 | ECLM Request File Content                                                             |

### TABLE 18 – NMEA PROTOCOL OUTPUT MESSAGES

### Note:

1. Not transmitted by default, can be enabled by \$PSRF103 command

### **NMEA Input Messages**

| NIVILA III put iviessages |                                        |                                                    |  |

|---------------------------|----------------------------------------|----------------------------------------------------|--|

| Message ID                | Message                                | Description                                        |  |

| \$PSRF100                 | Set Serial Port                        | Set UART parameters and protocol                   |  |

| \$PSRF101                 | Navigation Initialization              | Parameters required for start using X/Y/Z          |  |

| \$PSRF103                 | Query/Rate Control                     | Query standard NMEA message and/or set output rate |  |

| \$PSRF104                 | LLA Navigation Initialization          | Parameters required for start using Lat/Lon/Alt    |  |

| \$PSRF105                 | Development Data On/Off                | Development Data messages On/Off                   |  |

| \$PSRF106                 | Select Datum                           | Selection of an alternative map datum              |  |

| \$PSRF107                 | Extended ephemeris propriet            | ary message                                        |  |

| \$PSRF108                 | Extended ephemeris proprietary message |                                                    |  |

| \$PSRF110                 | Extended ephemeris debug               |                                                    |  |

| \$PSRF114,0x16            | ECLM start download                    |                                                    |  |

| \$PSRF114,0x17            | ECLM file size                         |                                                    |  |

| \$PSRF114,0x18            | ECLM packet data                       |                                                    |  |

| \$PSRF114,0x19            | ECLM Get EE Age                        |                                                    |  |

| \$PSRF114,0x1A            | ECLM Get SGEE Age                      |                                                    |  |

| \$PSRF114,0x1B            | ECLM Host File Content                 |                                                    |  |

| \$PSRF114,0x1C            | ECLM Host ACK/NACK                     |                                                    |  |

| \$PSRF117                 | System Turn Off                        |                                                    |  |

| \$PSRF120                 | Storage Configuration Setting          | 3                                                  |  |

|                           |                                        |                                                    |  |

TABLE 19 – NMEA PROTOCOL INPUT MESSAGES

### **19.2. OSP™**

OSP™ is a proprietary extension to SiRF Binary Standard protocol used by SiRF GPS processors.

### **OSP Binary Output Messages**

| MID<br>(hex) | MID (dec) | Definition                    | Sub ID (hex) | Sub ID (dec) | Definition |

|--------------|-----------|-------------------------------|--------------|--------------|------------|

| 0 x 02       | 2         | Measured Navigation Data      |              |              |            |

| 0 x 03       | 3         | True Tracker Data             |              |              |            |

| 0 x 04       | 4         | Measured Tracking Data        |              |              |            |

| 0 x 06       | 6         | SW Version                    |              |              |            |

| 0 x 07       | 7         | Clock Status                  |              |              |            |

| 0 x 08       | 8         | 50 BPS Subframe Data          |              |              |            |

| 0 x 09       | 9         | Throughput                    |              |              |            |

| 0 x 0A       | 10        | Error ID                      |              |              |            |

| 0 x 0B       | 11        | Command Acknowledgement       |              |              |            |

| 0 x °C       | 12        | Command No Acknowledgement    |              |              |            |

| 0 x 0D       | 13        | Visible List                  |              |              |            |

| 0 x 0E       | 14        | Almanac Data                  |              |              |            |

| 0 x 0F       | 15        | Ephemeris Data                |              |              |            |

| 0 x 10       | 16        | Test Mode 1                   |              |              |            |

| 0 x 12       | 18        | Ok To Send                    |              |              |            |

| 0 x 13       | 19        | Navigation Parameters         |              |              |            |

| 0 x 14       | 20        | Test Mode 2                   |              |              |            |

| 0 x 1B       | 27        | DGPS Status                   |              |              |            |

| 0 x 1C       | 28        | Nav. Lib. Measurement Data    |              |              |            |

| 0 x 1E       | 30        | Nav. Lib. SV State Data       |              |              |            |

| 0 x 1F       | 31        | Nav. Lib. Initialization Data |              |              |            |

| 0 x FF       | 255       | Development Data              |              |              |            |

### TABLE 20 – OSP BINARY OUTPUT MESSAGES

### **OSP Binary Input Messages**